算力存力Buff都叠满,至强6最强形态现身!

2024年是至强的大年。

先于6月正式发布的至强® 6700E系列开启了全新的、更为简洁命名方式:至强® 6能效核。144核的规格也意味着英特尔在最近几年当中首次在核心数量方面实现了领先。而且,这还并不是至强6的最强形态,毕竟大家都知道还有个6900P系列嘛。

9月26日,至强6这个“最强形态”终于正式发布,主要规格非常震撼。即使面对今年内晚于自己发布的其他厂商同级别CPU,至强® 6900P的已有规格也战力十足。

最强至强能有多强?

英特尔代号Birch Stream的新一代服务器平台所采用的至强6处理器是分批次发布的。6月发布的是代号Sierra Forest的能效核处理器6700E系列(E后缀即Efficiency Core,能效核的标记),目前发布的是代号Granite Rapids的性能核6900P系列。今年底和明年初还会陆续发布6900E、6700P,以及6500/6300等。未来的Intel 18A制造工艺的处理器,如Clearwater Forest,也会继续用于Birch Stream平台。

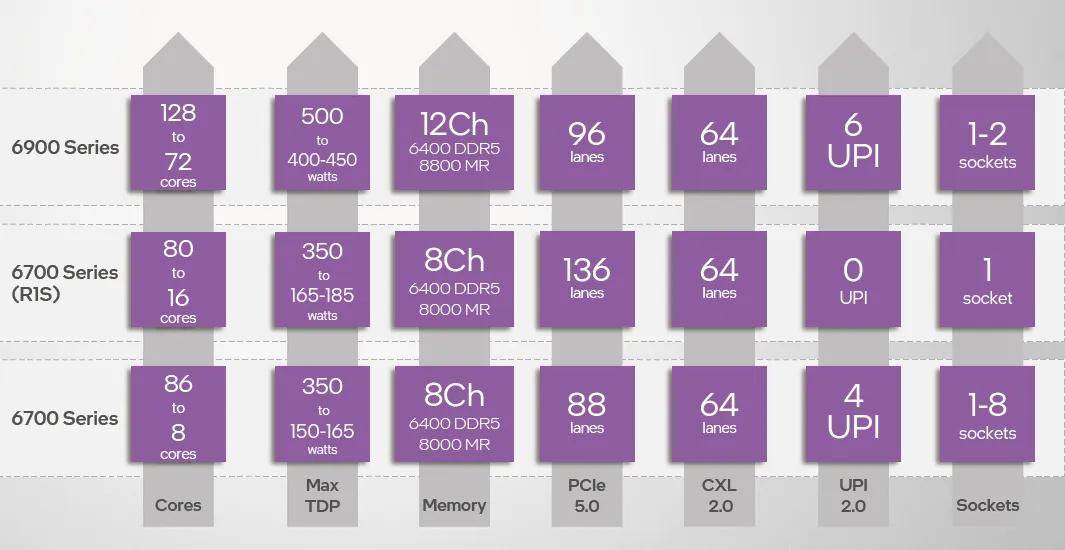

至强6900P是英特尔专为计算密集型工作负载设计的处理器,也是Granite Rapids的“完全体”。后缀的“P”意味其采用的是Performance Core,即性能核,规模大、性能强;6900的数字型号则说明其核心配置拉满——提供了72到128核的多种规格,TDP有400W和500W两种,组合成已公开5种型号,显得比较简洁。当然,依照惯例,云厂商等大客户还会有若干定制型号的。单就内核数量而言,6900P系列相对前两代“Rapids”产品线顶配的56/60(Sapphire Rapids)或64核(Emerald Rapids)直接翻倍!如此巨大的迭代幅度非常罕见,也难怪英特尔要改命名方式了,由表及里都透着一个意思:厚积薄发、脱胎换骨!

尤为值得一提的是:至强6900P也是业内首款性能核数量正式“破百”的产品,其他同级产品,不论是x86架构还是Arm架构都只达到了96核的水平。它们的性能核数量要追平英特尔,起码得等到下个季度。

随着内核规模增加,至强6900P的L3缓存达到了504MB。为了配合倍增的核数和显著提升的算力,至强6900系列的存力也大为增强,内存带宽方面不仅支持12通道DDR5 6400;并引入了新型内存MR DIMM,把数据率大幅提升至8800MT/s,基本内存带宽可以达到第五代至强可扩展处理器的2.3倍。另外,至强6还支持CXL 2.0,尤其是包括Type 3设备(也就是CXL内存),可以进一步扩展内存容量和带宽。

至强6900P的UPI2.0链路也有很大改进,速率提升到24GT/s,数量增加至6条,使得双路互联效率进一步提升。结合内核数量、内存带宽等方面的全面提升,至强6900P可以被视作高算力+高存力平台的最强机头,不论是科学计算,还是AI集群。根据已透露的测试,至强6900P平台的数据库、科学计算等关键应用负载的表现是上一代产品的2.31倍-2.5倍,AI应用性能是其1.83倍-2.4倍不等。

至强6的扩展能力也有不小的提升。其中6900系列单插座不论是性能核还是能效核均可提供96通道PCIe 5.0,双路即可提供192通道PCIe 5.0。未来上市的6700系列单路型号可以提供136通道PCIe 5.0,双/多路型号单插槽也可以提供88通道。相较而言,第四、五代至强可扩展处理器的PCIe 5.0通道数量为80。CXL支持能力方面,至强6 6900、6700系列都支持64通道CXL 2.0。

更多的内核、更多的内存通道、更多的PCIe通道需要更大规模的插座接口支持。 至强6带来了两种接口:LGA 4710和LGA 7529。至强6900系列使用面积较大的LGA 7529插座,提供最强大的内存带宽和扩展能力,是未来高性能、高密度服务器的基础。至强6700以及未来的6500/6300系列使用LGA 4710,尺寸与第四、五代至强的LGA 4677相仿,内存、PCIe的通道数相同或相近,有利于主流服务器内部布局习惯的延续性。

改进的EUV:Intel 3

核心规模的飙升首先得益于至强产品线终于获得EUV光刻机的加持。在2023年发布的酷睿Ultra已经率先使用了引入EUV的Intel 4制造工艺。而2024年发布的至强6则使用了进一步改良的Intel 3制造工艺。

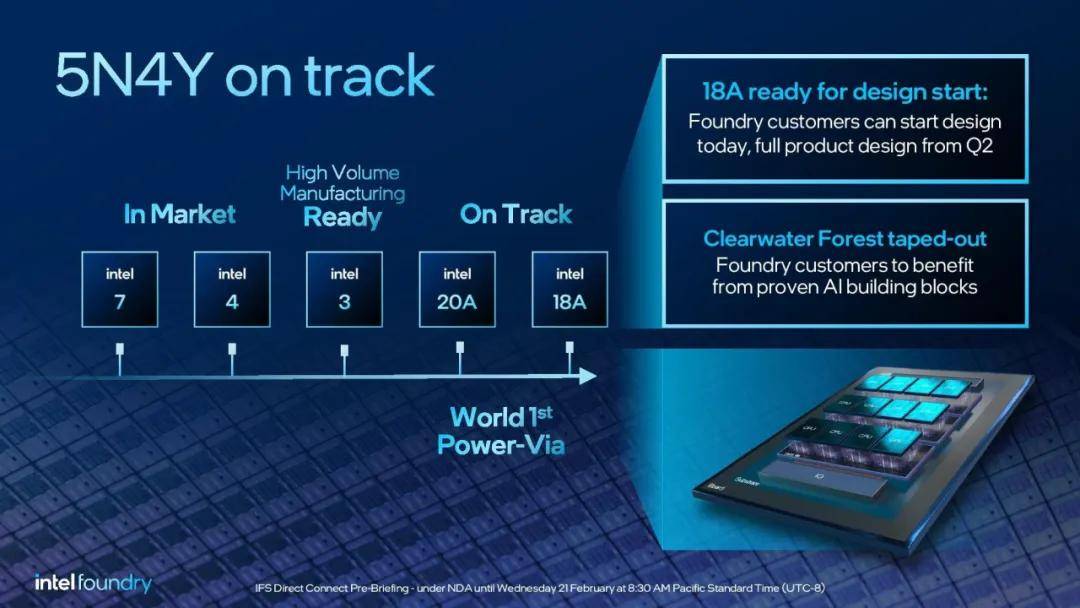

2021年7月,英特尔CEO帕特·基尔辛格公布了“四年五个制程节点”(5N4Y)的工艺路线图。Intel 3的量产时间节点位于2023年底,节奏基本符合计划。从基于Intel 4制造工艺的酷睿Ultra的市场表现看,EUV的加持确实明显提升了英特尔处理器的竞争力。至强6所采用的Intel 3制造工艺相对Intel 4可以规划更多的金属层、拥有更多细分版本。

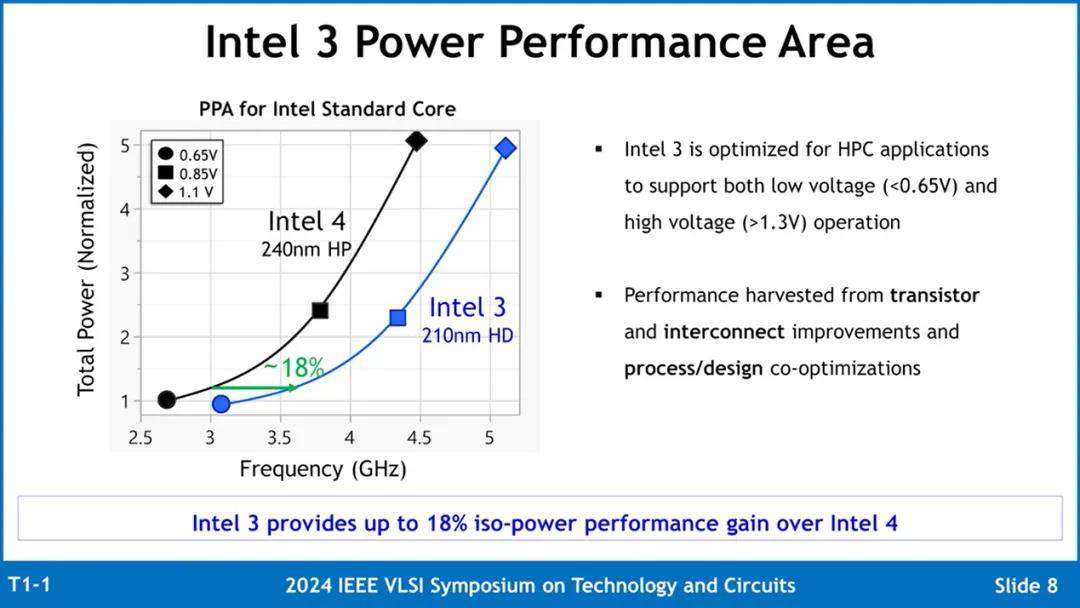

Intel 3在更多的步骤中应用EUV光刻,可以提供更密集的设计库、更高的晶体管驱动电流。Intel 3还有三种变体,包括3-T、3-E和3-PT。Intel 3、3-T是基本工艺,主要用于CPU;3-E是功能扩展;三者都支持TSV;Intel 3的这三种变体与Intel 4相比可以提升18%的性能功耗比。而3-PT进一步增加混合键合的支持能力,带来了更高的性能并且易于使用。Intel 3所有四种节点变体都支持240 nm高性能和210 nm高密度库,而Intel 4只支持240 nm高性能库。

对于性能取向,Intel 3针对高性能运算进行优化,可以支持低电压(<0.65v)和高压(>1.3V)运行,且在各电压下的频率均高于Intel 4。

微架构大迭代

至强6900P采用的性能核微架构代号Redwood Cove。Redwood Cove也是近年来英特尔最重要的微架构迭代,不但给服务器产品线带来了新名字,在消费类产品线同样开启了新的命名序列酷睿Ultra。

我们先快速回顾一下Redwood Cove的上一代Golden Cove/ Raptor Cove。Golden Cove其实也是非常重要的迭代,在消费类开启了大小核时代(第12代酷睿处理器),在服务器上就是第四代至强可扩展处理器。Golden Cove相对其前代的微架构大幅度提升了前端:

指令TLB翻倍,从128条增加到256条;

指令提取带宽从每周期16字节翻倍到32字节;

解码器从4路扩展到6路;

微操作缓存从2304条增加到4096条;

其他L1 BTB、L2 BTB等也有所提升。

Golden Cove的后端当然也有提升,譬如重排序缓冲区、分支目标缓冲区也有大概30%左右的提升,只是相对前端幅度不那么大。

Raptor Cove的微架构与Golden Cove差异不大,表现在实际产品上主要是缓存的提升,如基于Raptor Coved的第13代酷睿(Raptor Lake)的每核心L2缓存从12代(Alder Lake)的1.25MB提升到2MB;第五代至强可扩展处理器(Emerald Rapids)和第四代(Sapphire Rapids)每个核心的L2缓存都是2MB,但前者每个网格的末级缓存(Last Level Cache,也可继续俗称为L3缓存)从后者的1.875MB猛增到5MB。

Redwood Cove相对Golden Cove/ Raptor Cove的最重要变化是:

指令缓存从32KB增加到了16路、64KB;

微操作队列从144个条目增加到192个条目;

指令执行延迟降低;

更智能的预取和改进的BPU;

L2缓存的带宽有所提升;

AMX增加FP16支持。

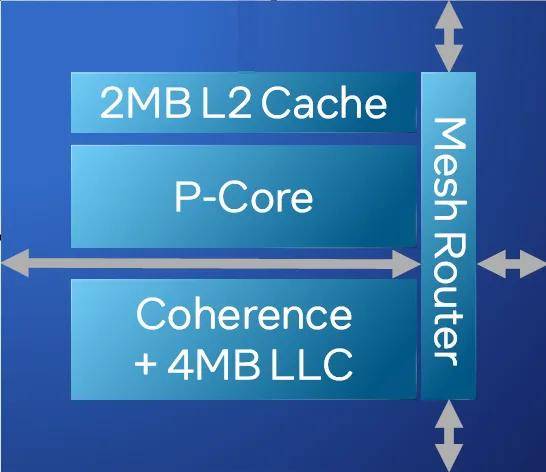

当然,Redwood Cove还有一个重大的优势就是“命好”,也就是前面提到的EUV制造工艺。但即使有革命性的制造工艺加持,至强6性能核也没过分扩张每个内核的规模。就至强6性能核的内核而言,每个网格节点是一个P核,每个P核配置私有的2MB L2缓存,以及共享的4MB 末级缓存。虽然平均到每个核的缓存容量并不比上一代至强(Emerald Rapids)多,但胜在总核数翻倍后。至强6性能核每个处理器可共享的末级缓存总容量依旧达到504MB,远超第五代的320MB和第四代的112.5MB。

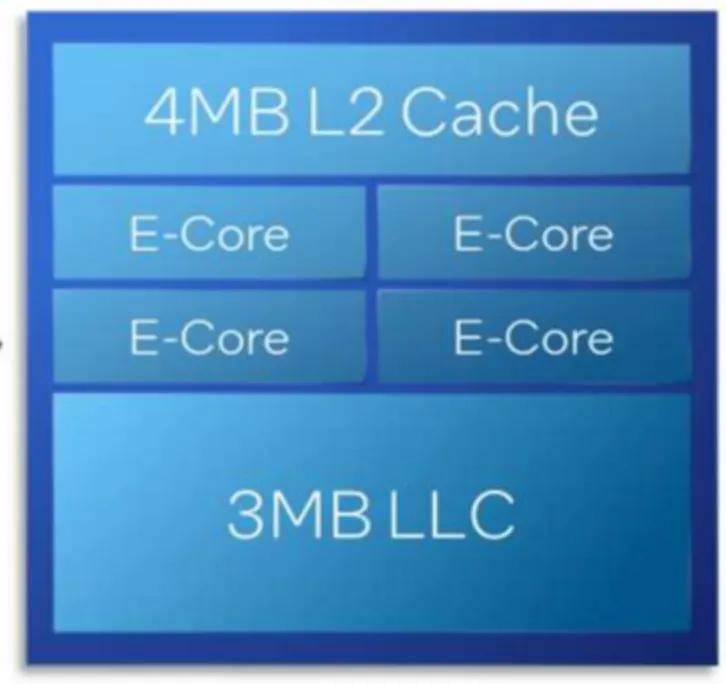

在此也顺便提一下至强6能效核的微架构Crestmont。这个微架构同样出现在了酷睿Ultra的能效核当中。Crestmont是2或4个内核为一组共享L2缓存。在至强6能效核当中,每2或4个内核与4MB的L2缓存(在酷睿Ultra中则为2MB)构成一个模块,这几个内核共享频率和电压域。这个模块对应的网格还拥有可整个处理器全部内核共享的3MB的末级缓存。换句话说,虽然至强6能效核的核数更多,但实际上网格规模比至强6性能核小。

能效核的指令缓存与性能核都是64KB,但数据缓存分别是32KB和48KB。前端的指令解码器宽度也有差异,分别为6和8宽。指令乱序执行引擎差异较大,能效核是256条而性能核是512条。能效核不支持性能核所支持的AVX-512和AMX,这也可以明显减小矢量运算单元的晶体管占用,但代价是每周期的单精度浮点运算次数有了数量级的差异。但能效核也改进了AVX2,增加了VNNI的INT8和BF16/FP16快速转换,这样在处理AI应用的时候表现也还有所改善。另外,其256位加密和1024/2048密钥也获得了能效核的支持,确保至强6平台的安全水平基本一致。

缓存规模、前端宽度以及矢量单元的差异,使得至强6性能核和能效核有不同的定位。早先发布的至强6能效核更适合微服务等运算强度相对较轻,可在高核心数量和规模扩展方面收益的任务,以追求更高的能效、更高的机架利用率。而现在发布的至强6性能核更适合大数据、建模仿真等计算密集型和人工智能任务,为高性能优化,单颗处理器的功耗直飚500W——当然,跟同期发布的Gaudi AI加速器的新品或类似的加速器产品相比,能耗是应有的代价,有能力提升性能上限才是正经事。

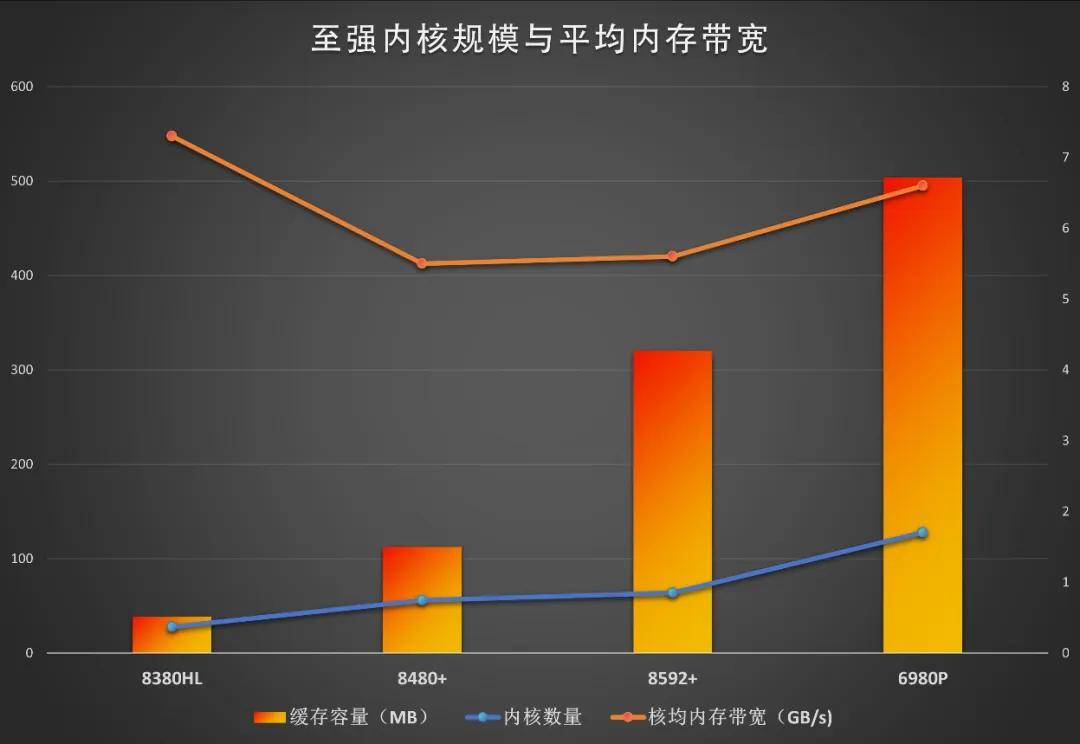

内存性能大跃进

内存(DRAM)的数据存储依赖电容,这个特点使其微缩和提速的难度大于晶体管。因此内存并没有沾摩尔定律的光,带宽和密度的增长落后于CPU、GPU的发展。内存带宽滞后于CPU内核数量的增长导致一个长期问题:平均每个内核的内存带宽增长乏力,甚至出现倒退。譬如第三代至强可扩展处理器内核数28,内存是八通道DDR4 3200,理论上的内存总带宽为205GB/s,平均每核7.3GB/s;四代是56或60核,内存八通道DDR5 4800,总带宽307GB/s,平均每核5.5GB/s;五代提升到DDR5 5600,内核再增加到64,平均带宽改进甚微。第四、五代至强可扩展处理器虽然引入了新一代的DDR5内存,但由于内核数量相对三代翻倍,内存带宽的增长幅度还是跟不上。同时期其他厂商的CPU核数在屡屡跃进的过程当中也存在同样的问题。为了弥补内存带宽增长较慢的问题,第四代至强可扩展处理器给部分用于科学计算的型号引入了HBM,五代则大幅度增加了末级缓存的容量,并支持CXL 2.0内存扩展。

在至强6900P上,内存问题终于得到了比较好的解决。这涉及三个角度:

1.大容量末级缓存。前面提到过,6900P每个网格提供4MB L3,总容量达到了504MB,分别是四代的4.5倍、五代的1.6倍。而且,至强的全网格架构使得任意内核访问末级缓存的延迟相比其他厂商的一些产品有更优的表现,例如不需要跨计算单元而造成延迟剧增。这种架构效率更高的优势也是至强在核数曾落后的情况下还能打的有来有往的关键原因。

2.DDR5内存双管齐下提升带宽。至强6900系列支持12通道DDR5 6400,总带宽可以达到614GB/s,平均每核的带宽大致还有5GB/s的水平。6900P还支持新型内存MRDIMM,频率提升至8800MT/s,总带宽达到了845GB/s,平均每核6.6GB/s,也明显超过了前两代产品,大幅度逆转了内核数量增加、平均内存带宽不升反降的问题。

MR(Multiplexed Rank)DIMM打开了DDR内存性能提升的新方向。DRAM通常由1到2个Rank组成,每个Rank的位宽为64位,如果考虑ECC,那就会有72或80位,但有效的数据是64位。消费类内存(UDIMM)可能只有1个Rank(颗粒数量较少的情况下),但追求大容量的服务器内存(RDIMM)基本上都至少有2个Rank。在以往的内存模式当中,一次只读取一个Rank的数据,另一个Rank暂时闲置时可以做刷新操作,以保持数据——这种轮流读取、刷新Rank的特点延续了多年。MRDIMM设计了一个数据缓冲区,通过将两个内存Rank分别读入这个缓冲区,再从缓冲区一次性传输到CPU的内存控制器,由此实现了带宽翻倍。第一代DDR5 MRDIMM的目标速率为8800 MT/s,其实每个Rank只相当于4400MT/s。现在DDR5 6400已经开始普及,因此MR DIMM的第二阶段目标是达到12800 MT/s,预计在2030年代的三代会提升至17600 MT/s。

3.CXL 内存扩展。第四代至强可扩展处理器开始引入CXL支持,当时是1.1版本,暂时也没有公开支持Type 3设备(也就是CXL内存)。从第五代开始正式引入了CXL 2.0,包括Type 3,可以帮助扩展内存容量和带宽。在至强6上,CXL设备的应用将更为普及,关键的CXL2.0标准设备,以及后向兼容的CXL1.1设备,预计都会陆续涌现。

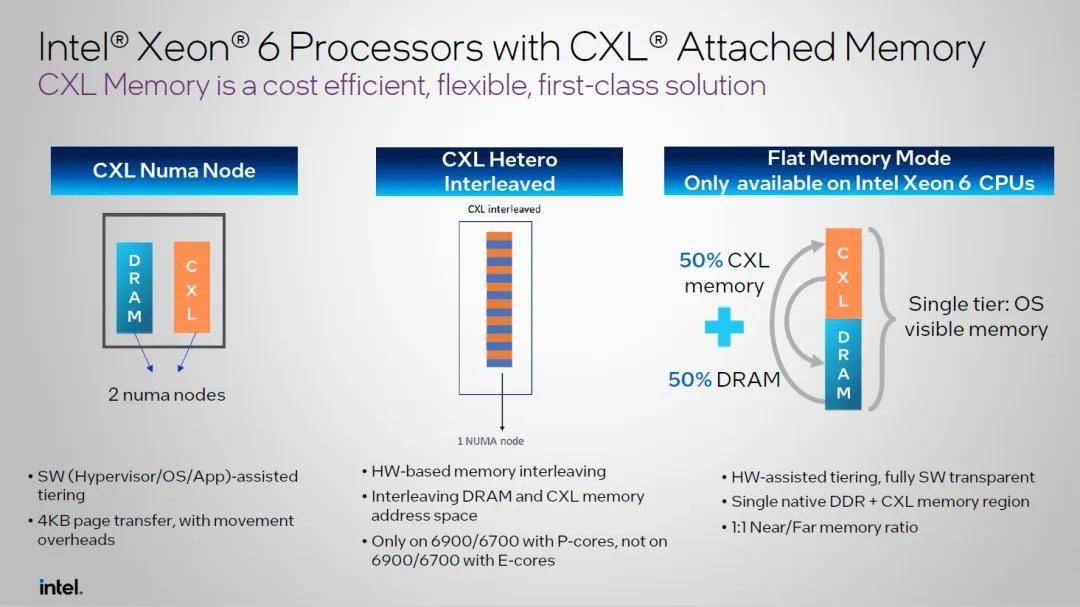

这里重点说一下CXL内存的优势。CXL2.0支持链路分叉,使一个主机端口可以对接多个设备,而且提供更强的CXL内存分层支持,可实现容量和带宽扩展。至强6支持3种CXL内存扩展模式:CXL Numa Node、CXL Hetero Interleaved、Flat Memory。

在CXL Numa Node模式下,系统的标准内存和CXL扩展内存被视为两个独立的Numa节点进行控制。每个Numa节点都有自己的内存地址空间,系统软件或应用程序可以将任务分配到不同的Numa节点,从而优化内存的使用。CXL Numa Node模式适用于需要精细内存管理的应用,可以通过操作系统、虚拟机管理程序(Hypervisor)或应用程序本身来辅助分层管理内存。

Hetero Interleaved(异构交织)模式通过将系统的标准内存和CXL内存混合在一起,形成一个统一的Numa节点。每个内存地址空间中的数据可以交替存储在DRAM和CXL内存中,从而均衡内存带宽,减少延迟。异构交织模式适用于对内存带宽有高需求的应用,特别是当需要将DRAM和CXL内存结合使用时。此模式只有在配备性能核的至强6700P、6900P上才支持。假设将每颗至强6900P的64通道CXL用满,可以额外增加256GB/s的内存带宽,单处理器就可以实现TB级的内存带宽,还是相当可观的。

Flat Memory(平面内存)模式下,CXL内存和标准内存被视为单一的内存层,操作系统可以直接访问统一的内存地址空间。硬件辅助的分层管理可以确保常用数据优先存储在标准内存中,次要数据存储在CXL内存中,从而最大限度地提升内存使用效率。平面内存模式最大的价值在于无需修改软件即可利用CXL内存扩展,而且这种模式适用于所有的至强6处理器。但平面内存模式要求标准内存和CXL内存是1:1配置,这略为限制了硬件采办、升级的灵活性。整体而言,平面内存模式是至强6时期最易用、收效最直观的模式,有望成为CXL内存扩展的主要模式。

踏上Chiplet异构之路

至强6是至强家族首次将计算和IO芯片独立,再通过Chiplet形式封装在一起,总算是把高级封装的优势真正发挥出来了。

第四代至强可扩展处理器是英特尔的首个Chiplet设计的至强处理器。其XCC版本内部是4颗芯片通过10组EMIB对等连接,每颗芯片提供15个内核、2通道内存控制器、1组加速单元,以及UPI、PCIe PHY若干。另外,还可以通过EMIB封装4颗HBM。

第五代至强可扩展处理器使用2颗芯片封装而成,所使用的EMIB数量明显减少,相应地也节约了芯片面积。虽然内核数量略有增加,但也损失了UPI、PCIe的数量,也不再能够搭配HBM。

随着制造工艺演进,偏重计算性能和晶体管密度的处理器内核,与偏重高速信号互联的IO控制器对制造工艺的要求产生了差异,因此,典型的Chiplet设计将计算和IO分离,分别应用不同的制造工艺。英特尔在14代酷睿上便采用了这种方式,分为Compute Tile、SoC Tile、IO Tile、Graphic Tile。代号Ponte Vecchio的英特尔Data Center GPU Max利用Foveros和EMIB技术,将47个小芯片封装在一起,包括Compute Die、Base Die、Rambo、IO Die等。

至强6终于也拆分成计算单元(Compute Tile)和IO单元(IO Tile),分别由Intel 3和Intel 7工艺制造。

计算单元

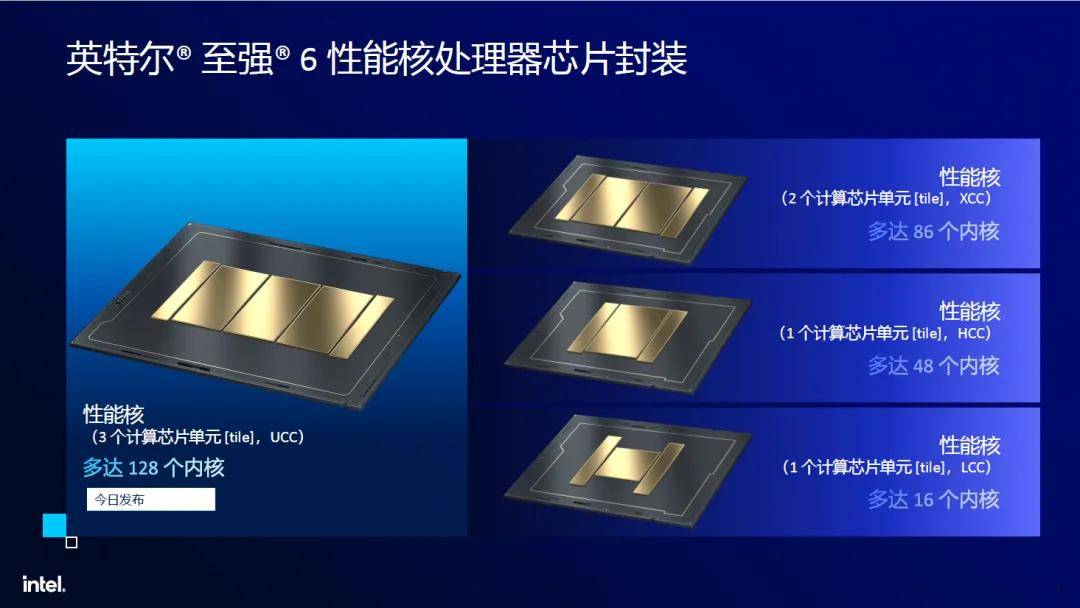

根据收集到的信息,对于能效核,目前只出现了一种计算单元的设计,每个单元最多提供144个内核、4组内存控制器共八通道;对于性能核,则是有三种计算单元的设计,可分别用于组合高核数、中等核数、低核数的规格。

至强6900P使用了三个计算单元,每个单元43个内核、两个内存控制器,总共构成129个内核(只使用128个)和12个内存通道。这种计算单元姑且称之为单元A,三个单元A构成的处理器被称为UCC。

未来发布的6700P核数跨度会很大,其中单路型号规划为16~80核,多路型号为8~86核。单元A有4个内存通道,两个单元A组合可以提供最高86核,下限应该不低于48核(否则屏蔽的内核数量就实在太多,也太浪费EMIB成本),这种规模的处理器被称为XCC。48核以下的中等核数被称为HCC,使用一种专门开发的单元B,每个单元提供48个内核和4个内存控制器。HCC核数的下限预计在24核左右。8和16核的6700P被称为LCC,需要使用第三种单元C,16个内核和4个内存控制器。

通过使用3种计算单元进行组合,至强6性能核可以构建跨度从8~128核的、非常绵密的规格。也许会有人认为,相比其他厂商只用一种规格计算单元实现扩展的设计,英特尔需要设计三颗不同的芯片的成本会更高。但我认为,这是英特尔优先考虑性能的结果。首先,至强6将内存控制器安排在计算单元中,离内核更近,延迟更低,即使因此牺牲了单元组合使用的灵活性也是值得的。其次,至强6性能核给不同规模的内核数量规划不同的网格规模,有利于降低核间的延迟,甚至,有可能LCC会针对较低的核数改用环形总线。综上,预计至强6性能核相对同等规模的其他厂商的产品依旧可能会拥有内存延迟低、缓存延迟低的优势。

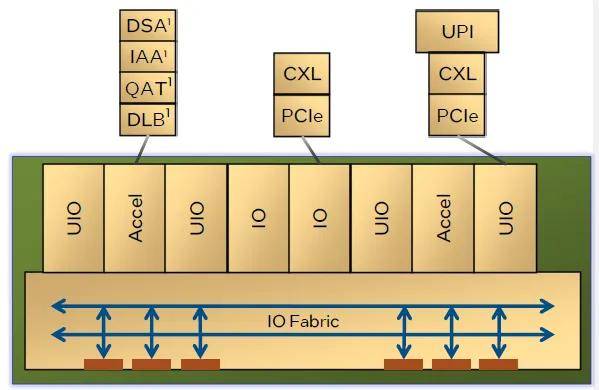

IO单元

IO单元方面,至强6900、6700系列都使用2颗相同的IO芯片。每个IO芯片由2个IO模块、4个UIO模块、2个加速器模块,以及IO网络接口构成。每个IO模块提供x16 PCIe或CXL连接;每个UIO模块提供x24 UPI2.0,或复用为x16的PCIe或CXL;每个加速器模块提供DSA、IAA、QAT、DLB加速器各一个。

以这次发布的至强6900P为例,两个IO单元总共提供8个UIO和4个IO模块。其中6组UIO负责提供6个UPI2.0互连,剩余的2个UIO和4个IO模块正好提供6×16=96通道的PCIe 5.0。双路至强6900P的UPI不但速率高(24GT/s,高于五代的20GT/s和四代的16GT/s),连接数量也提升了50%。

对于还未发布、也是主力产品的至强6700系列,估计由于要使用规模较小的插座,只提供最多4组UPI用于多路的互联,PCIe通道也有所缩减。但即使如此,至强6700系列的单路型号在将所有UIO配置为PCIe之后,单插槽就可以提供多达136个PCIe通道,或64通道CXL。如果用单路至强6700配合半宽主板构建双节点服务器,那一个机箱内的PCIe/CXL扩展能力(272 /128)远远超过已知的任何双路服务器。这种机箱可能会成为新的池化形态,可以更高的密度提供NVMe存储、CXL内存、加速器等。

结 语

由于英特尔在14nm到10nm制造工艺的迭代过程遇到了一些问题,以致此前几代至强平台在“核战”(比拼核数)中略显被动,但这个局面在至强6上有望完全逆转。改良后的EUV制造工艺看来没有束缚至强6的实力,核心数量、缓存容量、内存带宽等关键指标全都进入领先行列,一句话总结就是算力和存力的表现全部拉满。至强6900P系列在各种项目的测试当中,其代际性能提升就都是以倍数计,而非百分之十几、几十的进步。这种形势也使得英特尔得以全面竞争科学计算、大数据、AI等领域的性能王座。

此外,至强6终于实现计算与IO的解耦,也让至强6及未来的产品线走上了正确、灵活的道路,得以充分发挥Chiplet的优势。将Chiplet视作降低成本、提高良率的手段是狭隘的。Chiplet的价值在于灵活、复用、重构。英特尔长期以来很注重细分市场的耕耘,产品线非常复杂,正确利用Chiplet可以达到事半功倍的效果。我们非常期待至强6后续产品的陆续发布能够给业界带来什么样的想象力。

免责声明:市场有风险,选择需谨慎!此文仅供参考,不作买卖依据。

标签:

相关阅读

精彩推荐

阅读排行

相关词

- PGG眼部按摩仪礼物意大利前总理马泰奥·伦齐传递美好情谊

- 千万不要小瞧肌肤炎症,让杜莎之谜小黑瓶还你无暇肌肤

- 俞敏洪与李佳琦同道歉 直播行业不能卡在低价和IP滥用上

- 江苏扬州:独领风骚30年“扬稻6号家族”让“饭碗”端得更稳

- 高质量发展调研行丨小苹果创出产业大天地——陕西洛川苹果产业集群见闻

- 江苏徐州:专精特新“新变量” 产出高质量发展“新增量”

- 河北发现完整“热河生物群”恐龙化石

- 新语丨用好短视频,讲好中国故事

- 亚运会前看浙江|助燃运动热情,传递爱与希望——杭州亚运会火炬手谈“薪火”相传

- 导出来PDF损坏原因有哪些

- 弹窗提示zxpsignlib-minimal.dll丢失如何解决

- 如何解决电脑提示migisol.dll文件丢失的问题?

- 提示加载witnesswmiv2provider.dll错误解决方法

- 江苏淮安:办好民生实事项目 优化群众出行条件

- 促进房地产市场平稳健康发展 多个二线城市全域取消限购政策

- 江苏无锡:守住“生态本底”,让绿色成为高质量发展鲜明底色

- 小米私密文件误删找回方式是什么

- iphone15边框变窄了没有

- 2023国际青年设计师邀请赛周五开赛 居庸关长城“跨界” 变身时尚设计舞台

- “福运武清”乡村振兴主题文学创作采风活动举行

- 手提电脑开机蓝屏没反应解决方式有哪些

- 眉笔净含量1克价格或超黄金,李佳琦说的“不贵”到底贵不贵?

- 更多优质项目在柯桥步入快车道

- 8月社会融资规模和人民币贷款均实现同比多增

- ltool6.dll文件丢失如何修复?

- 青海40名订单定向医学生签订就业协议

- 1至8月铁路运输业三大指标稳步增长

- 促进文明交流互鉴 2023世界大河文明论坛将在郑州举行

- 2023中国民营企业500强发布:京东、阿里、恒力位居前三

- “盐”值出众,一见倾心,彰显“最盐城”文化的魅力

- 陕西洛川:一颗苹果背后的“产业链”发展

- iphone15pro和14pro的区别

- 重庆:七项任务提升基层能力

- 未来与李佳琦合作模式是否会有变化?花西子:不回复

- 天舟五号撤离空间站 完成多个空间应用项目实验

- ebueula.dll修复方法

- 天舟五号撤离空间站组合体

- 闪耀暖暖绚彩星梦活动介绍

- 电脑磁盘故障怎么恢复

- 出生“一件事”长三角跨省通办

- c盘文件恢复后打不开了怎么办

- 华为mate60pro芯片哪里生产

- 《上古纷争》英雄介绍 暗系诅咒虚弱「洛基」

- 数字里看发展 我国教师队伍结构不断优化、素质不断提升

- 潭牛文昌鸡:打造文昌鸡产业“海南样板”

- 内蒙古巴彦淖尔环境综合治理显成效 “塞外明珠”被“擦亮”

- 河北省兴隆县举办2023年“质量月”活动启动仪式

- 青岛—加德满都航线正式开航

- 土豆骑士好玩吗 土豆骑士玩法简介

- 三亚拟对35条街道进行精品化建设改造

- 四川省资阳市特检所开展工业管道安全隐患排查

- 如何修复遭损坏cserhelper.dll方法

- 重庆市北碚区市场监管局用好“三面镜子”保障群众“两节”食品安全

- 狂欢,以啤酒的名义!2023儋州青岛啤酒节即将火热开启

- 比亚迪海豹DM-i重磅上市

- 未来智能豪华轿跑阿维塔12全球首秀

- 湖北机场集团与杜福睿集团签订合资合作协议

- 海南航空无陪儿童服务升级,安心呵护服务“可视”

- 华为手机如何给财神爷上香

- 从“制造”走向“质造”!长沙启动“质量月”活动

- 提示wshqos.dll丢失报错如何解决

- 杭州新开迎亚运重点航线 直飞迪拜、阿拉木图

- 2023年“诚信兴商宣传月”启动仪式成功举办

- 文字玩出花美装天梯怎么过关 文字玩出花美装天梯通关攻略

- 山东:打造中医药传承创新“齐鲁路径”

- 嘉善赴上海专场路演科创项目

- 万联证券:化妆品行业个股业绩表现分化 静候需求端修复

- 命运方舟寂静岛岛之心怎么获取 命运方舟寂静岛岛之心获取方法

- 安信证券:原油有望高位震荡带动上游资本开支 油服行业景气向好

- 临高开展客车整治行动

- 美邦股份可转债募资必要性合理性存疑

- 二〇二三年国家网络安全宣传周开幕式举行

- 上海37家市级医院开启科普宣传周

- 重庆市巴南区“四个重点”开展电子计价秤专项整治行动

- 虚销“空气粮” 私卖“升溢粮” 假购“增数粮”

- 中信建投:8月社融超预期 三大拐点确立下银行股估值将明显修复

- 今年“月饼圈”斑兰成“新宠” 海南多家企业推出“斑兰月饼”

- 难忘师生情 华夏航空开展教师节空地活动

- 别走错!广州地铁这个站点出入口有调整

- 《宝可梦:大集结》火焰鸡新演示 9月14日上线

- 《动物派对》发布联动“白菜狗”预告视频 推出联动皮肤

- 山东 | 山水禅心,锦绣五莲

- 《漫威蜘蛛侠2》因为版权问题纽约没有克莱斯勒大厦

- AR手游《怪物猎人Now》真人发售预告 9月14日上线

- 山西证券:8月汽车产销超预期 行业景气度继续提升

- 2023年国家网络安全宣传周网络安全博览会举办

- 10个重点行业稳增长方案发布

- 科普园地|复杂的三体问题存在上万个解决方案?

- 回暖!央行公布关键数据,释放什么信号?

- 央行:8月末社会融资规模存量为368.61万亿元,同比增长9%

- 《鬼灭之刃》派对游戏新作正式公开 2024年发售!

- 民营企业借力资本市场持续做优做强

- 中国中小企业发展指数连续3个月上升

- 汽车市场“淡季不淡” 促消费政策效应渐显

- CIOE 2023丨深挖场景价值,共连数字化美好未来

- 《女神异闻录 异空之塔篇》9月14日登陆Switch PC版稍后推出

- 《心灵杀手2》发布新8分钟实机视频 第三人称女探员战斗

- 《暗黑破坏神4》1.14补丁说明 赛季经验加成提升!

- 网传《GTA6》售价定为150美元 玩家们有点慌了!

- 《诱拐事件》steam页面上线 写实风格恐怖新游

- 第十二届“郑仙非遗文化月”开幕 6场系列活动等你来

- “潘鹤与新中国雕塑研究展”开幕

- 安徽宁国:畲乡晒秋庆丰收

- 为全球跨境投资提供“中国样本”

- 《Crisol: Theater of Idols》上线Steam 第一人称恐怖新游

- 中国中小企业发展指数连续三个月上升

- 上海崇明港西渔光互补光伏发电项目全容量并网

- 海珠区建筑联盟成立

- 《卧龙:苍天陨落》DLC“称霸江东”短片 新怪物可怕

- 2023绿色低碳创新论坛举行 科技部:将建碳达峰碳中和科技创新监测评价机制

- 增城|派潭“村晚”走进上九陂村

- 育碧免费FPS游戏《不羁联盟》延期 因未通过主机验证测试

- 《极限竞速:Motorsport》发布18分钟实机预告视频

- 2023世界智能网联汽车大会将于9月20日至24日在京召开

- 《消逝的光芒2》出现大量差评:禁用MOD、微交易!

- 江苏实现换电重卡跨城际多主体互通互换

- 利德治疗仪:高新技术领军,打造健康产业

- LPL:周淑怡恋情败露,得罪大量铁粉,与劣迹艺人拍拖,下场悲惨

- 北京发布地质灾害气象风险黄色预警

- 如何解决iasacct.dll加载错误问题?

- 广东将防汛Ⅱ级应急响应调整至Ⅲ级

- 广深城际9日停运56趟列车

- 3dmax2012缺少dll文件处理有哪些方法

- 孕期吃的比平时多很多,为什么还会贫血?常见于3种原因!

- 崩坏学园2负重提高途径推荐 崩坏学园2怎么提高负重

- 今明两天,海南岛部分地区有大到暴雨、雷暴大风!儋州最新天气

- 北京石景山发布暴雨黄色预警和地质灾害蓝色预警

- 就爱做蛋糕好玩吗 就爱做蛋糕玩法简介

- jpeg2000.dll重新安装的解决方法

- 中央气象台9月9日10时继续发布暴雨黄色预警

- Win11宽带连接方法

- 汽车销售模拟器好玩吗 汽车销售模拟器玩法简介

- 原神灵矩关湖宝箱在哪里-灵矩关湖宝箱在哪里介绍

- 保卫萝卜4新春厨艺秀第8关怎么过

- 罗马诺:尤文计划与拉比奥特商谈续约,球员合同明夏到期

- 我国科学家第一次在高山上发现陨石坑

- 抖音简笔画小人(抖音简笔画)

- 车库被淹,物业未及时通知挪车,要担责吗?法院判了!

- 人人都离不开工具!PPT之父去世:塑造现代社会信息沟通方式

- 新疆博湖县南美白对虾喜获丰收

- 穿越时光的“慢火车”,大山深处最美的风景

- 当“非遗藤编”走向世界

- 天命奇御战斗模式及八卦修炼系统体验心得 游戏通关心得分享

- “追梦少年”来到中国青年报 探秘“一张纸的力量”

- 开学季高校校长花式宠新:有的凌晨还在接机,有的亲手制作非遗糕点,还有的送上生日蛋糕

- 周杰伦天津演唱会发生意外?经纪公司凌晨回应

- 兰州通报“网民反映污水排入黄河”调查情况

- 电脑蓝屏后键盘鼠标都不亮怎么办

- 工业题材电影创作研讨会在京举办

- 房企动态|金泰樾系三子,金地清峯上、招商雲蘭营销中心开放!